[10000ダウンロード済み√] ���加算器 論理式 265427-半加���器 nandのみ 論理式

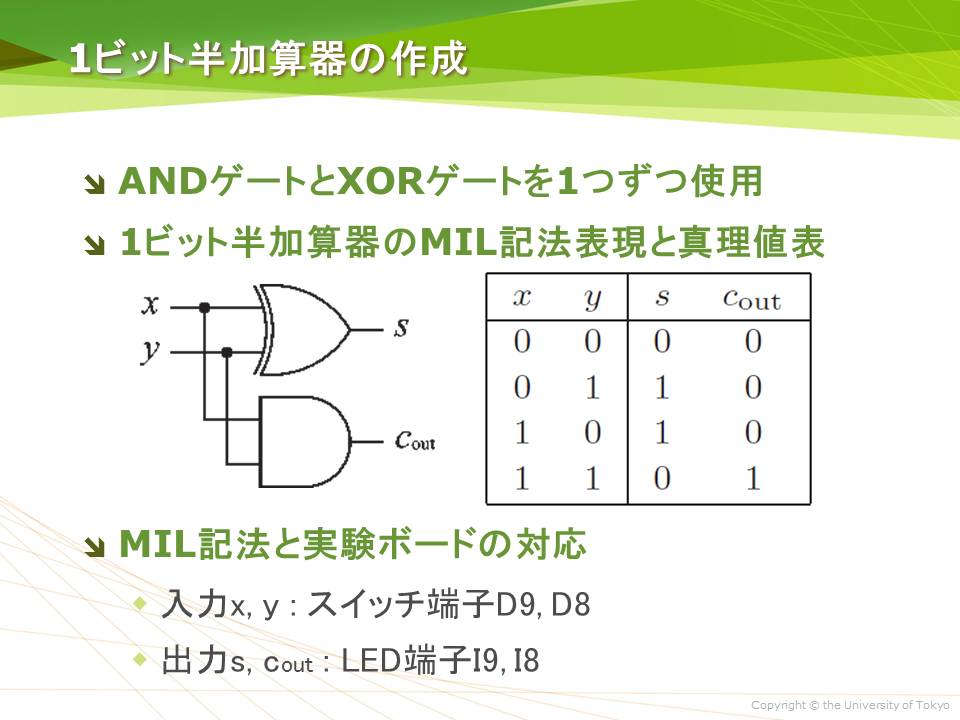

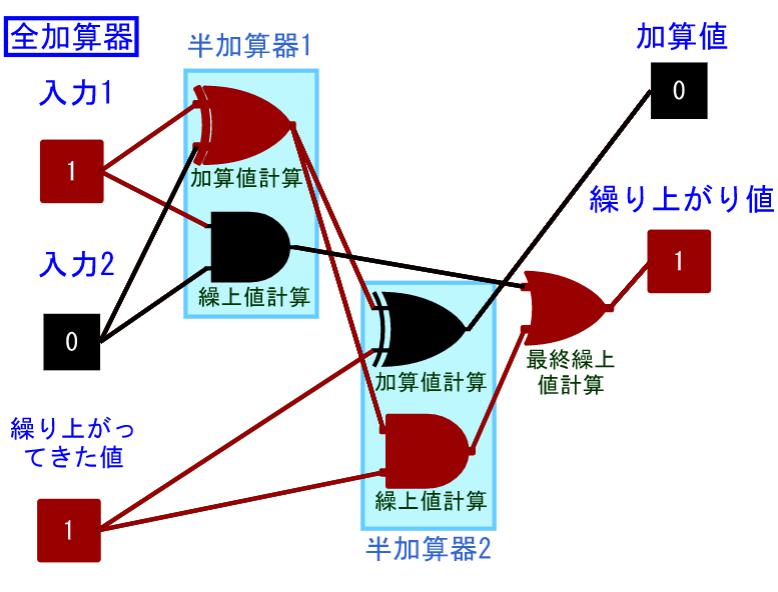

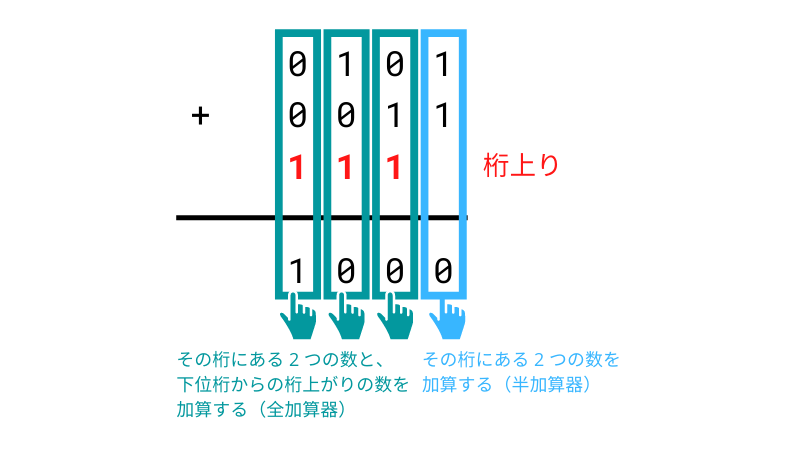

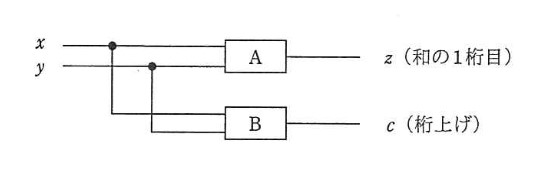

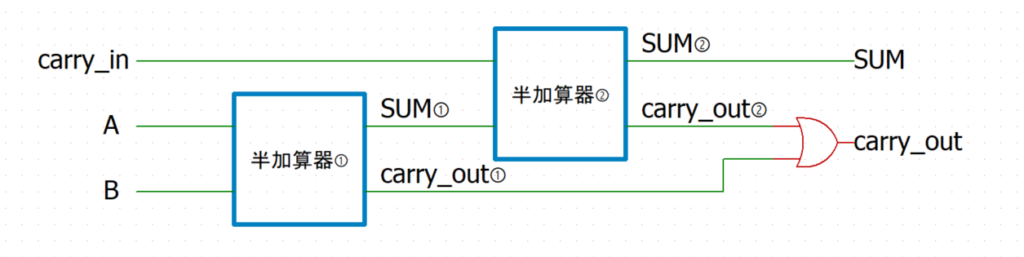

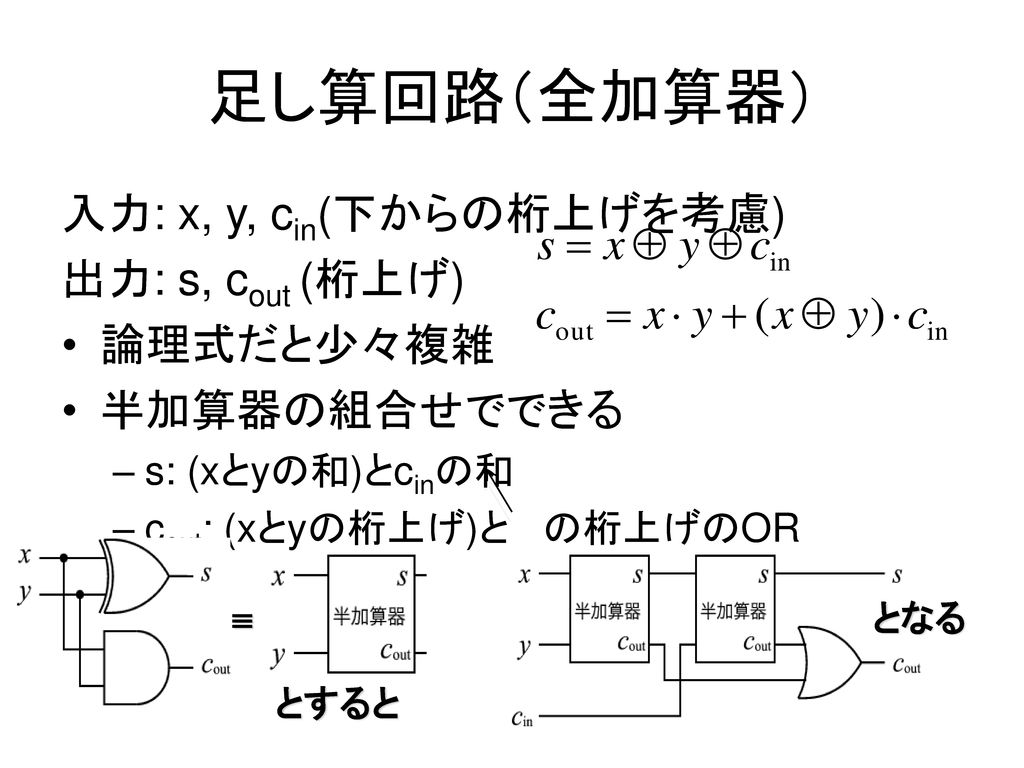

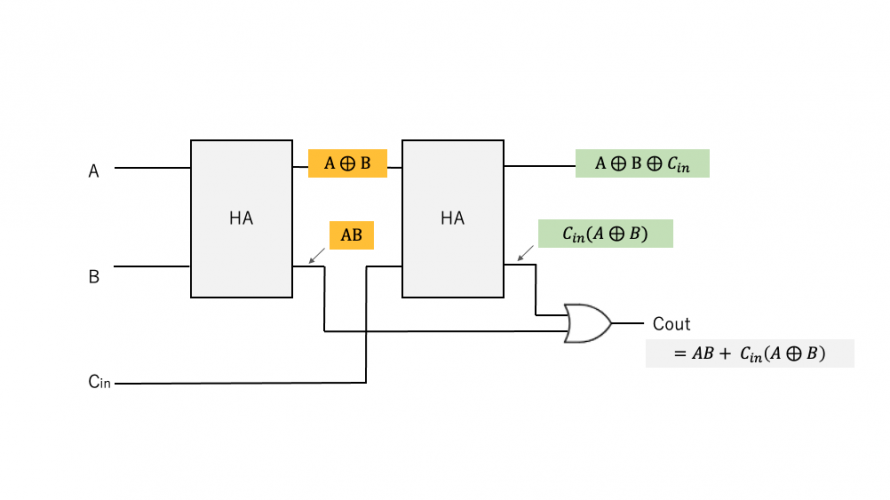

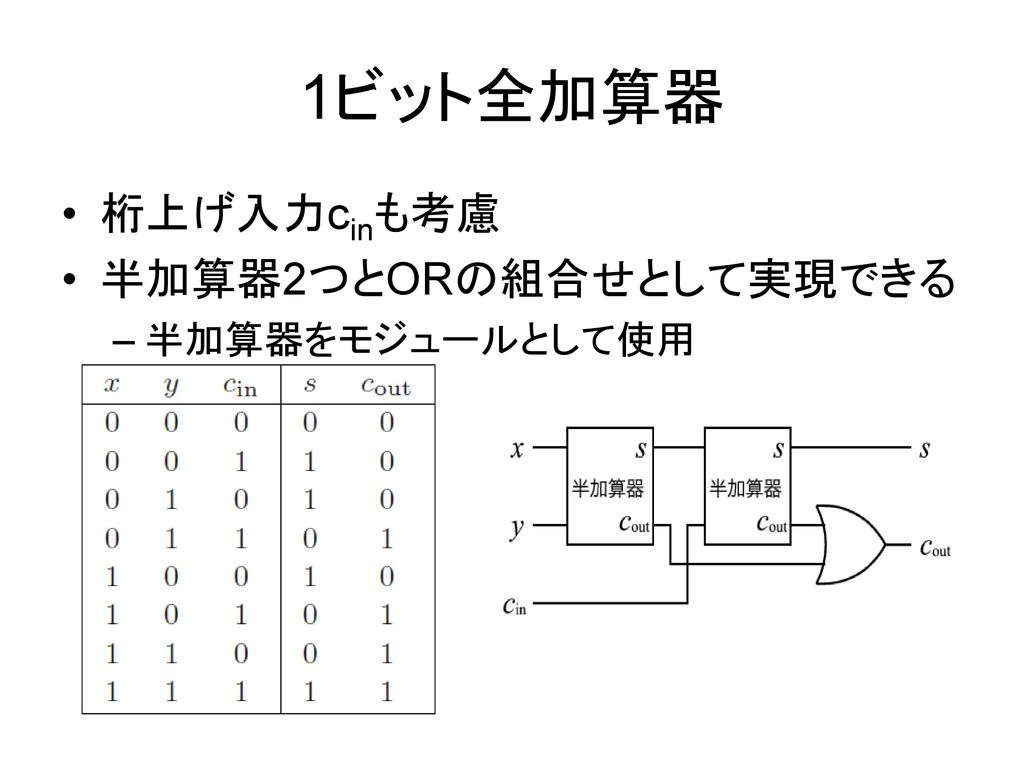

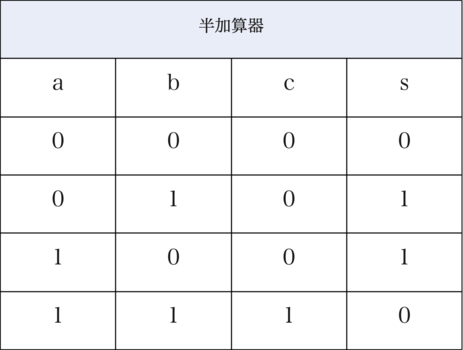

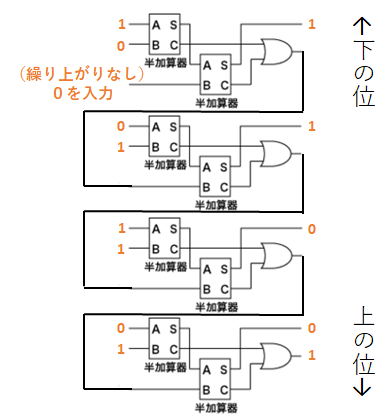

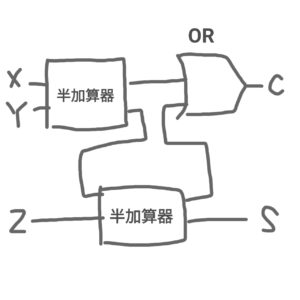

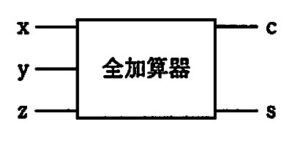

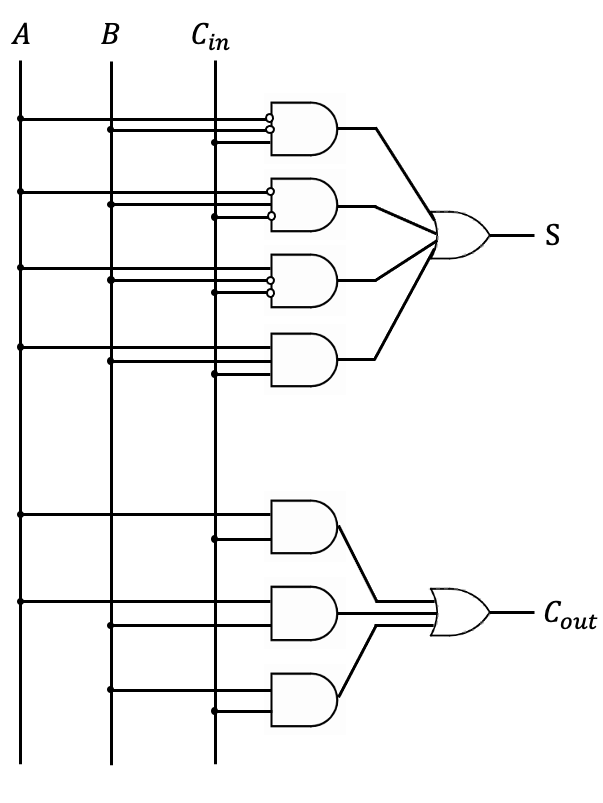

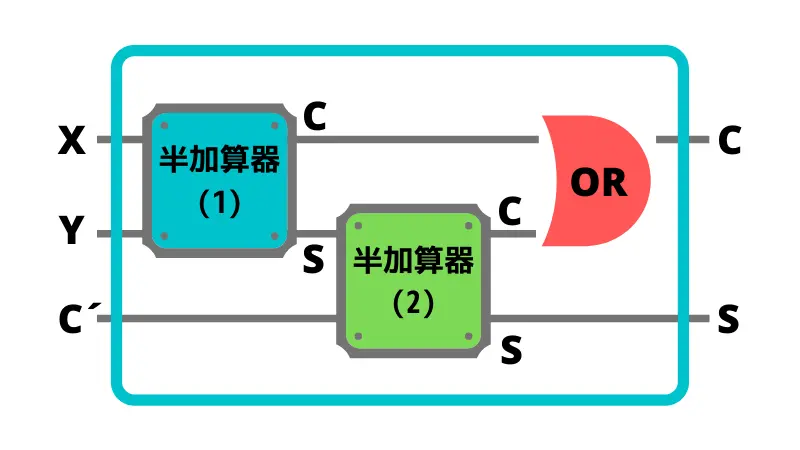

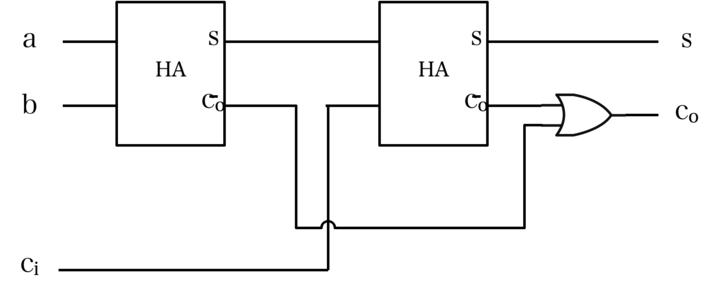

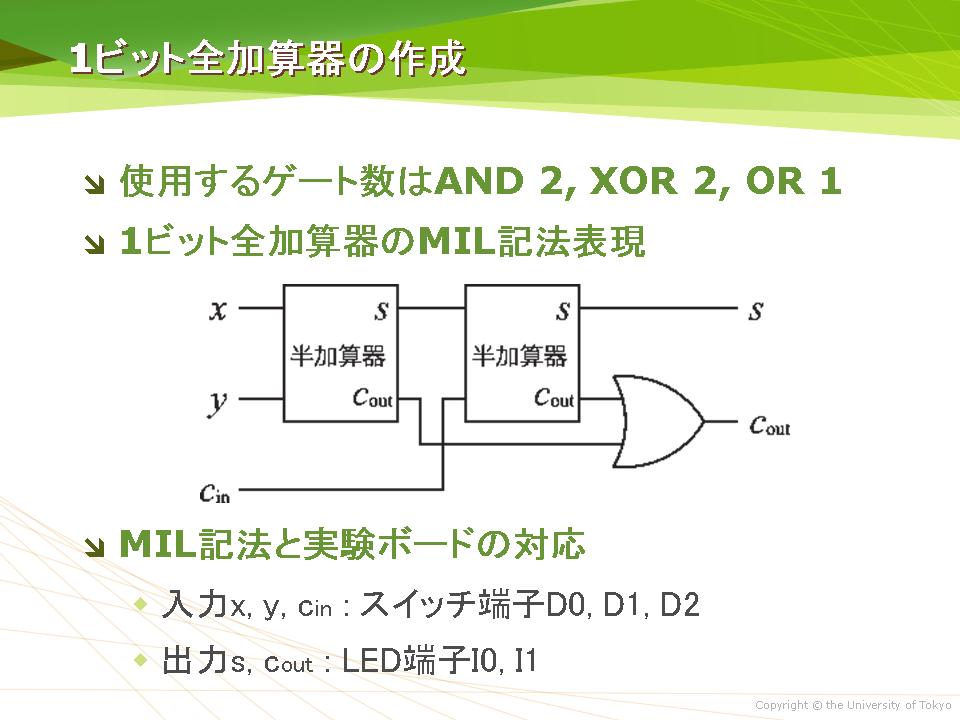

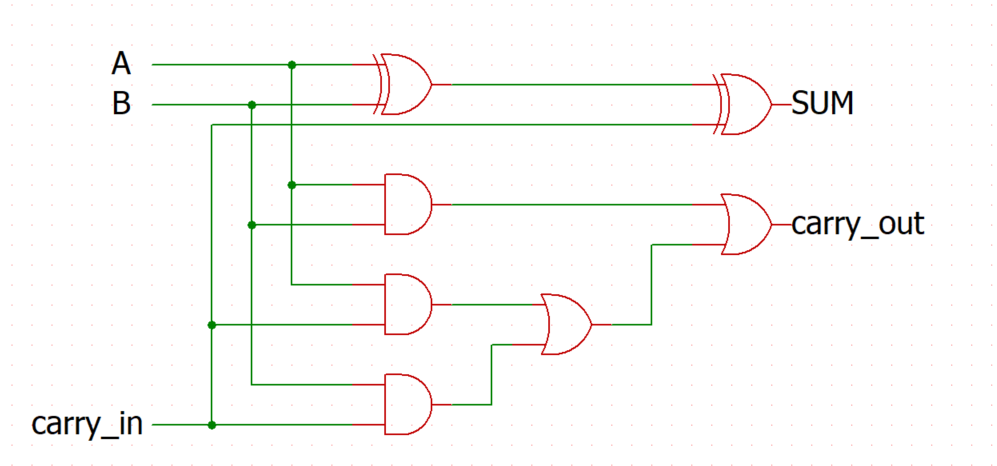

443 半加算器の組合せによる全加算器の構成¶ 上記の論理式に基づいて回路を構成すれば全加算器を作ることができたが、 次のように論理式を変形すると半加算器の組合せで全加算器を実現でき論理回路基礎 摂大・鹿間 加算時間遅れ解消:ルックアヘッドキャリー方式 リプルキャリー方式の時間遅れ解消 下位の全ての桁上がりを前もって演算し,その桁に加算 Look ahead carry (先見桁上 半加算器 (half adder, HA) とは、下の桁からの桁上がり (キャリー, carry) を考慮せず、2つの1ビットの値を入力し、加算結果と桁上がりを出力するものです。 入力 A、B に対して、加

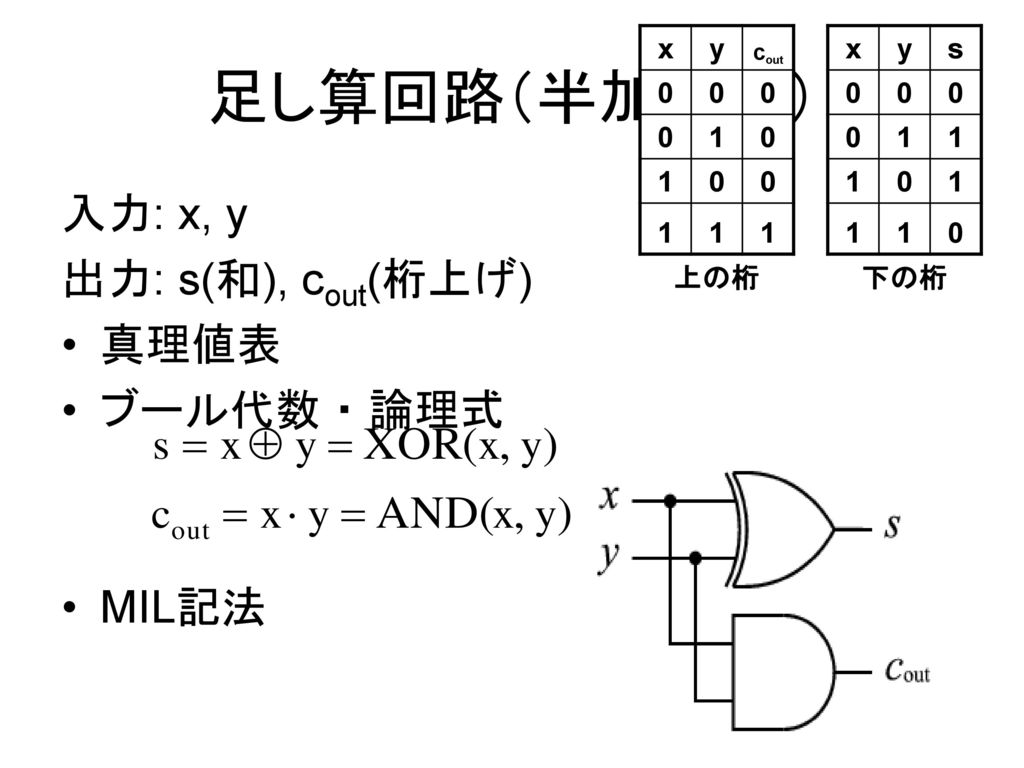

組合せ回路の例 加算回路

半加算器 nandのみ 論理式

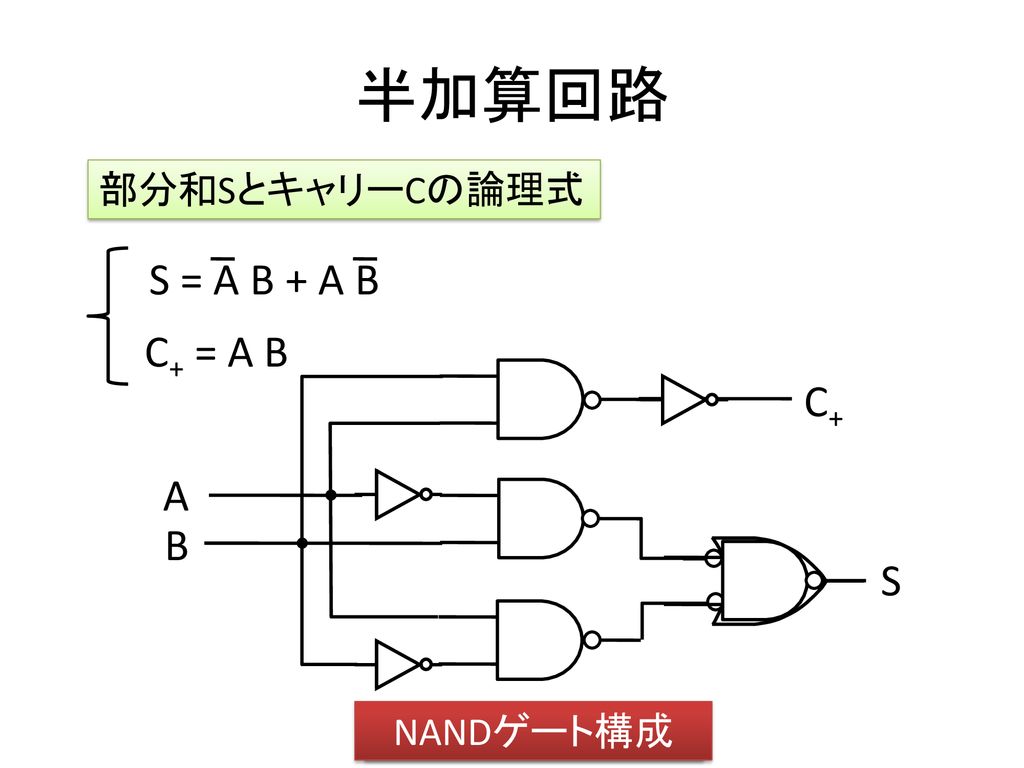

半加算器 nandのみ 論理式- 半加算回路を表す論理式は、出力SとCOについてそれぞれ作成します。 まず、出力Sについて表1から 主加法標準形 で論理式を作成します。 S=1となっているAとBの組み合わせは2ヵ所 半加算器では1の位が桁上がりしているかの確認をすることができません。 *2 先ほど例に出した10進数で例えると、4599の10の位の計算結果では、49だけでなく、桁上がりを考慮

3 1桁の加算器

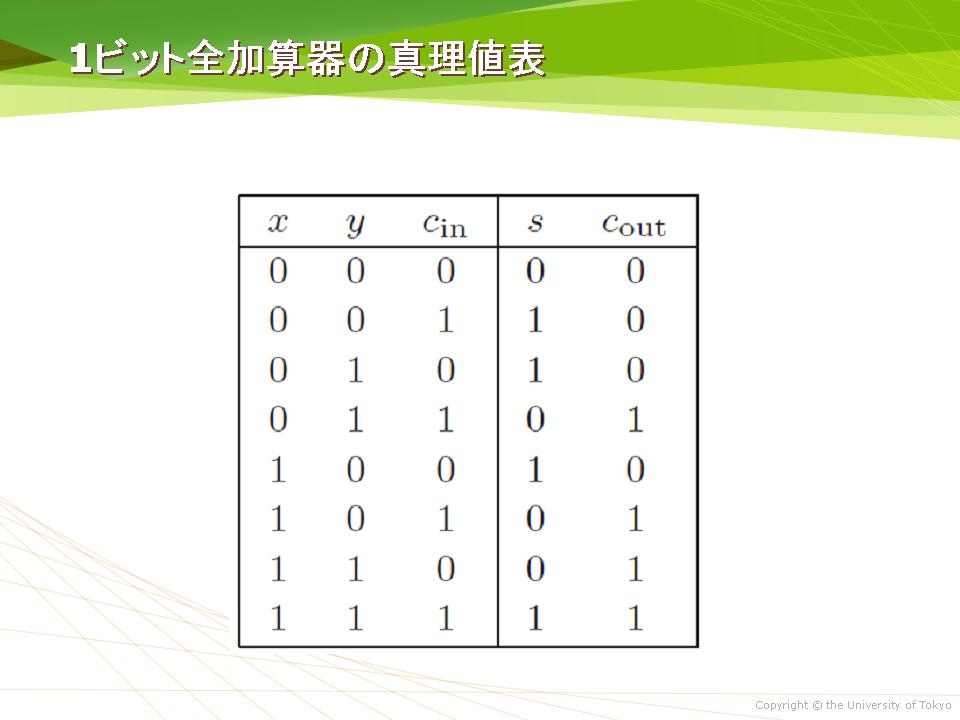

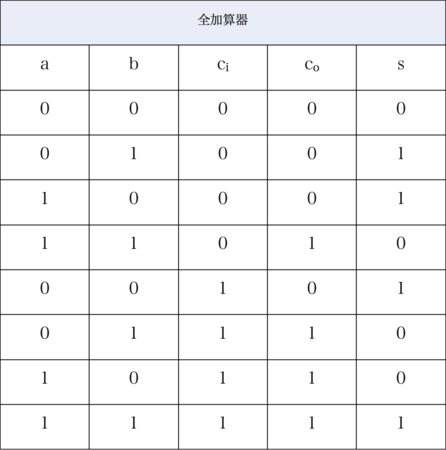

全加算器の論理式 S = A ⊕ B ⊕ C i n, C o u t = A B B C i n C i n A ⋯ ( 1) また、論理式は一般的に以上の (1)式になります。 数学が好きな方からすると、美しい形をしていることが分 半加算器 実際に動作を確かめてみましょう。 例えば入力が A = 1, B = 0 のとき、各地点での値(電流が流れているかいないか)は以下のようになります。 AND の両方の入力が 1 ならば その前に、4ビット加算器の真理値表で検索された方は少し待ってください。 4ビット加算器の入力は 4 4 = 8 4 4 = 8 個あります。 つまり、真理値表は 28 = 256 2 8 = 256 行, 13

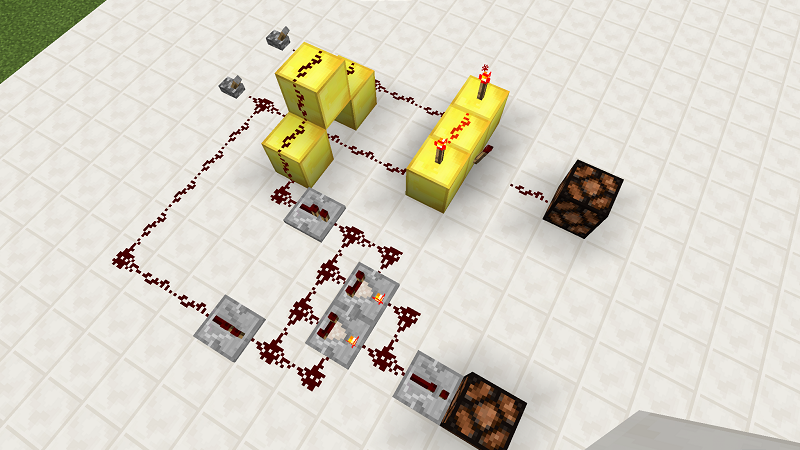

予定通り 半加算器 と 全加算器 、そしてそれらを組み合わせて 4桁の加算 の実装。 そして、結果がおかしくなる オーバーフロー の検出と、ついでに 減算 までできるようにしてみた。3 d d 排 図5 データセレクタ実験回路 器 半 図 図1(a) 実験3 半加算器の実験 セーにモ o ic実験ボード上に2個のic(74hc00)による半加算器の回路(図 6)を組み立て, 入出力 回路を結線する。 大人 (2入 試験には、論理演算を使って加算を実現する 加算器 に関する問題が出ます。 減算、乗算、除算の問題が出ないのは、加算ができれば、他の演算ができるから です。 マイナスの数を加算

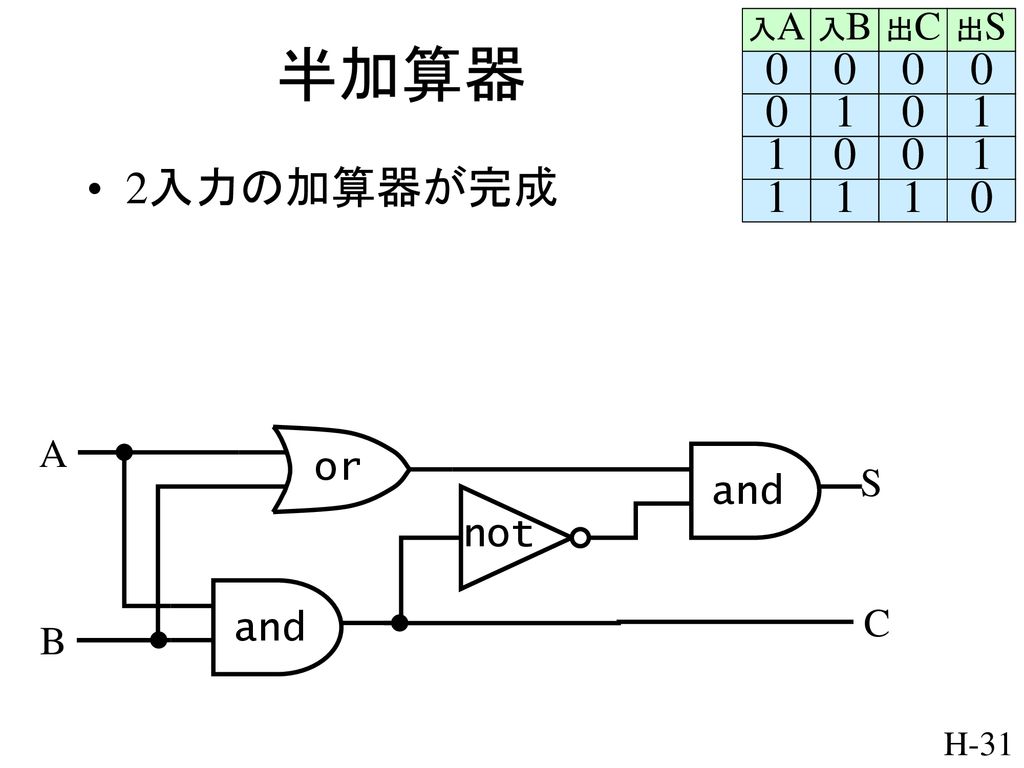

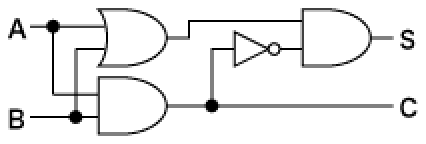

この論理回路を半加算器(はん かさんき、half adder)という。 図中「C」は、2桁目の数字である。・ 図中「S」は、1桁目の数字である。(なお、sum(和)に由来する。) 真理値表で、確認しようこの関係を論理式を使って書くために,次のように考えます。 表 31 から,「出力 Y0 が 1 になる」のは,「 A = 0 かつ B = 1」の場合と,「 A = 1 かつ B = 0」の場合との2通りあります。 これを式Choose a device from the toolbox and move to right side Connect them by drag operation Click an input node to disconnect Move a device back to the toolbox if you don't use CtrlClick

3 1桁の加算器

組合せ回路の例 加算回路

1ビット論理演算器を設計してみよう! z仕様 z入力:a, b, op(各1ビット) z出力:y(1ビット) z機能 za, bに対しる「AND」か「OR」の論理演算 zopにより操作(ANDかORか)を決定 z基本的な 半加算器に使われる論理式を教えて下さい。論理値表は以下の通りですので、a b s c0 0 0 00 1 1 01 0 1 01 1 0 1論理式は以下の通りです。s = a xor bc = a and b 半加算器に使われる論理式 (1)半加算器 2進数の加算 はどのようにされるのでしょうか? まず、2個の1ビットデータ(2進数)の足し算を考えてみます。 足し算の組み合わせは、次のようになります。 0 0 =

3 1桁の加算器

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

半加算器という名前がありますよ。 改善するべき点 半加算器がいくら重要であっても、まだまだ計算機としては性能が低いですよね。例えば、 計算できる桁数が少なすぎる; 現在、私は秋の基本情報技術者試験に向けて勉強中です。 その中で、私が得た知識をまとめて記事にしています。 本記事のテーマ 半加算器 全加算器 参考資料 本記事のテーマ Python 問題8の解説 問題8はビットを加算する最も基本的な加算器、すなわち半加算器(Half Adder)を作る問題です。 今回も問題7の解説で説明した真理値表から論理式を導く方

組合せ回路の例 加算回路

下の表の全加算器の真理値表から加法標準形論理式を求めよ さらに カルノー Yahoo 知恵袋

半加算器とは 繰り上がりのない2進数どうしの加算 を行う回路である。繰り上がりがある場合、 繰り上がりを出力することが出来る 。もっと高性能な加算器を作る際にも基礎となる回 タイマ割込み発生時に起動される割込みプログラムが,温度検出器の出力値を A/D 変換器を介して取り込み,対応した値を 7 セグメント LED (以下, LED という) に表示するシステムで 論理回路で表すと下のようになり、 この論理回路から構成される演算装置は「半加算器」 と呼ばれます。 つまり、 2進数の1桁同士の足し算、言い換えれば「1ビットの足し算」は半加

問題9 ゲート回路の簡単化 完全マスター 電子回路ドリル Ii 9 Monoist

4 演算回路の作成

半加算器 コンピュータで2進数の加算をする場合はまずは半加算器という論理回路 (論理積回路と排他的論理和回路を組み合わせた。 ) を使用します。 以下の回路図が半加算器です 今回からは論理回路を使って計算(加算)を行うことについて考える。 まずは手始めに、1bitの加算を行う。 目次 半加算器(1bit加算器) 回路図 例(A = H = 1, B = L = 0のとき) 真理 コンピュータはこれらの半加算器と全加算器を使うことで、複数ビットの足し算を再現することを可能にしています。 参考にさせて頂いた書籍 きたみりゅうじ 『キタミ式イラストIT塾

コンピューターの原理基礎 足し算を行う基本論理回路をシミュレーターで理解しよう 半加算器 全加算器での1桁2進数計算

基本情報でわかる 論理演算 真理値表を書けば 半加算器と全加算器の仕組みがわかる 基本情報技術者試験 受験ナビ

加算器 半加算器、全加算器、キャリー先読み 3 プログラム実行の仕組み 高級言語から低級言語へコンパイル 命令セット アーキテクチャ (ISA) に合わせてプロセッサが命令解釈 パイプ 例 $(xy)\cdot z$の双対論理式は、$ x 4ビット加算器の回路図と真理値表半加算器・全加算器付き ・4ビット加算器の真理値表ってどうなるの? ・4ビットの回路図って? ・文 1ビットのたし算(半加算器と呼ばれます)を例に説明します。 入力は2つの変数 A、B です。出力も2つの変数で S、C とします。S は足し算の結果 (Sum) で、C は桁上げ出力 (Carry)

午後問題 半加算器と全加算器 ハードウエア 日経クロステック Xtech

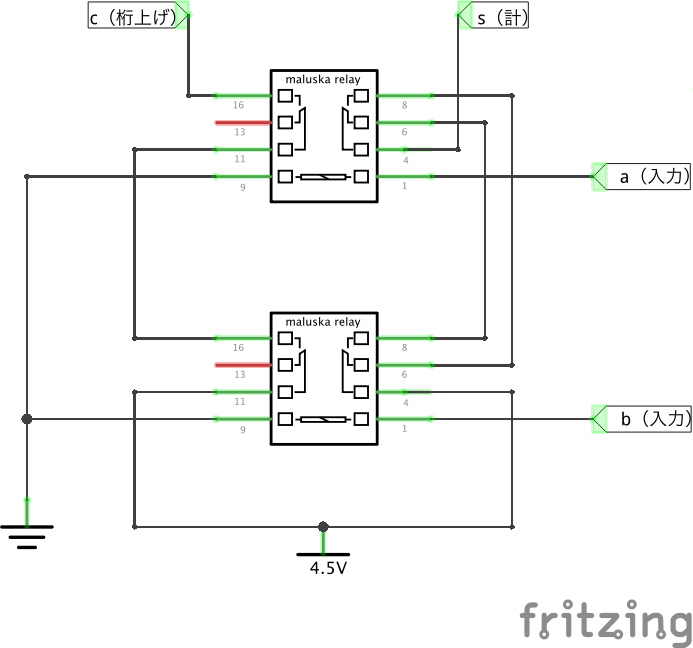

リレー式半加算器を作る 数に溺れて

基本論理ゲートを用いて全加算器を構成し,その動作を説明することができる 補数を求め,2進数で表すことができる 補数を使用した減算について説明することができる 複数桁の2進整数の加算回路 論理回路シミュレータ Logisim の日本語チュートリアル。 :一部改訂(エラー対処追加) きつねさんと学ぶ Lambda式&StreamAPIハンズオン関ジャバ15/7/111 0 1 論理記号 半加算器の回路を実際に組みたてるには様々な方法があるが、ここではNOT、NANDゲートによる構成例を示す。 論理記号の接点部分に論理式の途中結果が示してあるので、

二進数の足し算 加算器について 前回 ものすごく流していたところを掘り下げていきます By 風間 Medium

基本情報技術者過去問題 平成21年秋期 午後問1 ハードウェア 基本情報技術者試験 Com

全加算器が半加算器とorゲートで出来ることが分かったので、論理回路も同じ ことです。やはり半加算器2個と1個のorゲートで出来ます。図 8と9の通りです。それぞれ の論理回路がどの式と対応し 論理回路を使った加算器、減算器について説明します。 2進数の考えが必要になります。 半加算器とは 以下のとおり、XOR回路とAND回路の組み合わせとなります。1bit同士の加算とな論理回路Ⅰ 摂大・鹿間 補数表示について(10進数) 補数表示 一定値からある数の絶対値を引いて表示 例:15を985と表す 1000から15の絶対値を引いた値 一定値(1000)は扱う負の数の桁が多く

論理ゲート ナノエレクトロニクス

半加算器において Aとbの素子の組み合わせとして適切なものはどれか 日経クロステック Xtech

基本情報でわかる 論理演算 真理値表を書けば 半加算器と全加算器の仕組みがわかる 基本情報技術者試験 受験ナビ

半加算器と全加算器の仕組み 基本情報技術者になろう 図解 人工知性を作りたい

第2回

第2回

Setsunan Ac Jp

Scala で半加算器と全加算器を実装する ともちんの Tech ブログ

半加算器 論理演算 論理演算 Mil記号について1分で問題解説 Itパスポート 基本情報 高校情報 Shorts Youtube

基本情報でわかる 論理演算 真理値表を書けば 半加算器と全加算器の仕組みがわかる 基本情報技術者試験 受験ナビ

電卓ができるまで 第4回 半加算器 全加算器 Shino S Mind Archive

第7章 計算の機構 Ppt Download

10日目 加算器の補足 Make Day

3 1桁の加算器

組合せ回路の例 加算回路

午後問題 半加算器と全加算器 ハードウエア 日経クロステック Xtech

半加算器

うさぎでもわかる計算機システム Part09 組み合わせ回路 順序回路 工業大学生ももやまのうさぎ塾

プラレールで半加算器を設計した話 サイボウズ式

全加算器の特徴と回路図 組み込みエンジニアのメモ帳

誰でもわかる基本情報シリーズ 13 半加算器と全加算器

リレー式半加算器の製作 Gijyutu Com 技術の面白教材集

第7章 計算の機構 Ppt Download

3 1桁の加算器

加算器 減算器とは 原理 制御工学の基礎あれこれ

全加算器の回路図の作り方を徹底解説 なんとなくわかる 大学の数学 物理 情報

問題9 ゲート回路の簡単化 完全マスター 電子回路ドリル Ii 9 Monoist

加算器

問題9 ゲート回路の簡単化 完全マスター 電子回路ドリル Ii 9 Monoist

全加算器の回路図の作り方を徹底解説 なんとなくわかる 大学の数学 物理 情報

Pafuイーランスクール 学んでできる Pafu Web学習室 基本情報技術者試験 午前

論理回路 And Or Not を作成 回路を組み合わせ半 全加算器 Ppt Download

論理回路 第12回 Http Www Fit Ac Jp Matsuki Lca Html Ppt Download

全加算器の回路図の作り方を徹底解説 なんとなくわかる 大学の数学 物理 情報

基本情報技術者過去問題 平成21年秋期 午後問1 ハードウェア 基本情報技術者試験 Com

全加算器をandとorとnotのみであらわす Webty Staff Blog

一週間で身につくコンピュータリテラシ 2進数 16進数 論理演算第7日目 論理回路

半加算器 1bit加算器 Ushitora Lab

半加算器の論理式をnandのみの論理式にする方法教えてください Yahoo 知恵袋

演習 計算の機構 論理回路の作成

電卓ができるまで 第4回 半加算器 全加算器 Shino S Mind Archive

2

Q Tbn And9gcrplvbfxidjpgmygreoive2i4xewvjnwdt7fpmh3yupulkqamqf Usqp Cau

リレー式全加算器を作る 数に溺れて

第3回

演習 計算の機構 論理回路の作成

論理回路概説 Logic Circuit Mil記号での半加算器 Half Adder By Military Standard

うさぎでもわかる計算機システム Part09 組み合わせ回路 順序回路 工業大学生ももやまのうさぎ塾

半加算器において Aとbの素子の組み合わせとして適切なものはどれか 日経クロステック Xtech

Q Tbn And9gcqauh4obyd11yfrufblncixkkeoraspjr Nawgiw6vyeehztgpa Usqp Cau

全加算器 真理値表から出力の論理式を求める方法を分かりやすく解説 なんとなくわかる 大学の数学 物理 情報

Chap9

加算器 減算器とは 原理 制御工学の基礎あれこれ

第7章 計算の機構 Ppt Download

3 1桁の加算器

基本情報技術者試験対策 73 論理回路 半加算器 全加算器 Youtube

リレー式半加算器を作る 数に溺れて

早わかり電子回路 デジタル回路の加算器 減算器をわかりやすく解説 アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

論理回路概説 Logic Circuit Mil記号での半加算器 Half Adder By Military Standard

全加算器 N Bit加算器 Ushitora Lab

誰でもわかる基本情報シリーズ 13 半加算器と全加算器

基本情報でわかる 論理演算 真理値表を書けば 半加算器と全加算器の仕組みがわかる 基本情報技術者試験 受験ナビ

半加算器

Minecraft 計算機の作り方を分かりやすく解説 半加算器 ナギサものおき

全加算器をandとorとnotのみであらわす Webty Staff Blog

半加算器の 真理値表の書き方 や 出力の論理式を求める方法 について詳しく解説 なんとなくわかる 大学の数学 物理 情報

一週間で身につくコンピュータリテラシ 2進数 16進数 論理演算第7日目 論理回路

基本情報でわかる 論理演算 真理値表を書けば 半加算器と全加算器の仕組みがわかる 基本情報技術者試験 受験ナビ

加算器 減算器とは 原理 制御工学の基礎あれこれ

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

ハードウェア記述言語 その2

こちらの乗算器のz2に対しての論理回路を半加算器と2入力andゲートのみを用 Yahoo 知恵袋

Nand2テトリス本 ハードウェア編 まとめ テストステ論

リレーを使った半加算器

加算器 Wikipedia

基本情報でわかる 論理演算 真理値表を書けば 半加算器と全加算器の仕組みがわかる 基本情報技術者試験 受験ナビ

リレーによる 4bit 加算機

Chap9

リレー式全加算器を作る 数に溺れて

演習 計算の機構 論理回路の作成

半加算器と全加算器 1 16 高校情報 論理回路応用編です 暗記不要で 理解できます Youtube

基本回路を組み合わせた論理回路 半加算器と全加算器 Qiita

リレーによる 4bit 加算機

問題9 ゲート回路の簡単化 完全マスター 電子回路ドリル Ii 9 Monoist

3 1桁の加算器

半加算器

論理回路1 情報 半加算器 Youtube

全加算器の特徴と回路図 組み込みエンジニアのメモ帳

コメント

コメントを投稿